High-Speed image sensor integrating parallel image compression circuits

We have developed image compresion algorthm that is suitable for high-speed CMOS image sensor.

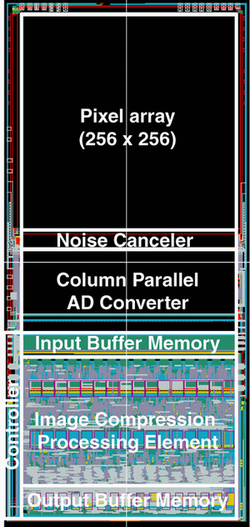

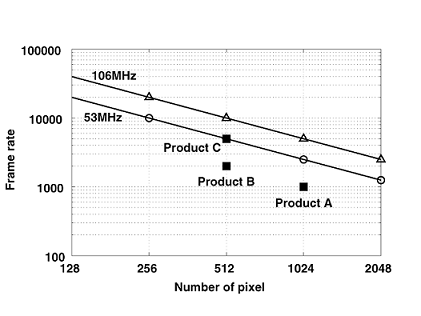

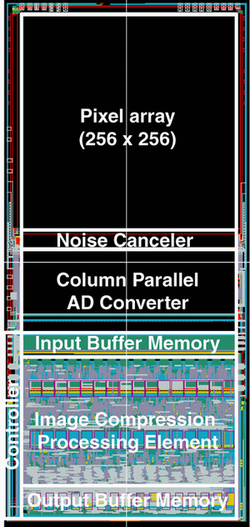

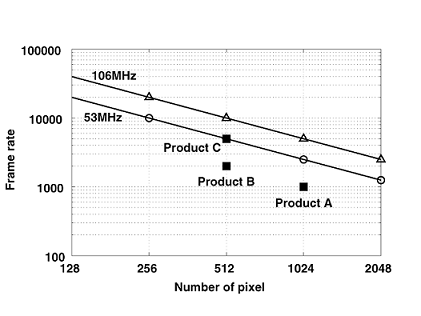

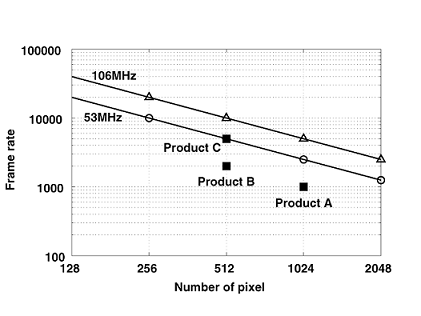

A 10,000 fps high-speed image sensor with 256 x 256 pixels can be realized

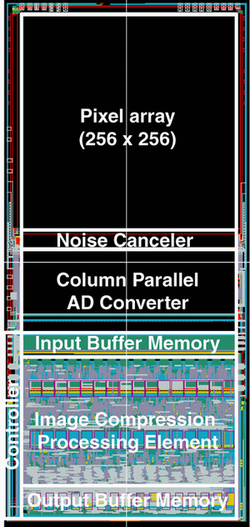

by integrating 16 image compression processing elements. A prototype high-speed CMOS image sensor

shows the effectiveness of the proposed on-sensor

image compression circuit for acheving a high-frame-rate and a high resolution image sensor with a relatevely small area.

|

|

| Layout of prototype image sensor.

| Relationship between frame rate and number of pixel.

|

References

- Y. Nishikawa, S. Kawahito, T. Inoue, " Parallel image compression circuits for high-speed cameras", Proc. SPIE Proc. Electronic Imaging, vol.5671, no.14, Jan. 2005.

- Y. Nishikawa, S. Kawahito, "A parallel image compression system for high-speed cameras, Proc. IEEE Int. Workshop on Imaging System and

Techniques, pp.53-57, May. 2005.

- Yukinari Nishikawa, Shoji Kawahito, Masanori Furuta, Toshihiro

Tamura, "Design of Parallel Image Compression Circuits for High-Speed CMOS Image Sensors", The Journal of the Institute of Image Information and Television Engineers, vol.61, no.3, pp.369-377, Mar. 2007.

[Home] / [Research project]

Copyright(C)1999-2007, Imaging Devices Laboratory

e-mail: [email protected]