画像圧縮高速度イメージセンサ

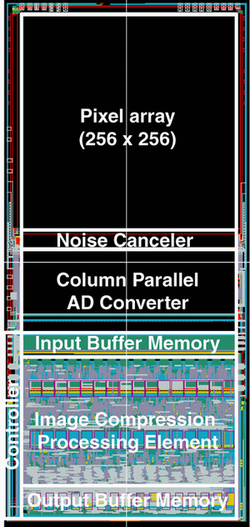

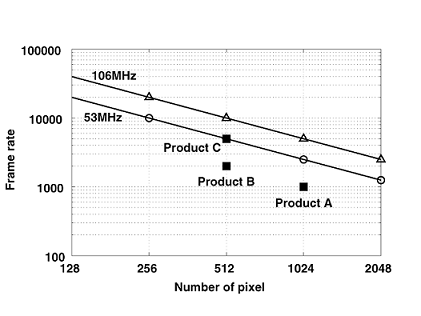

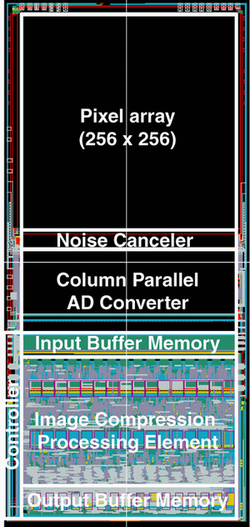

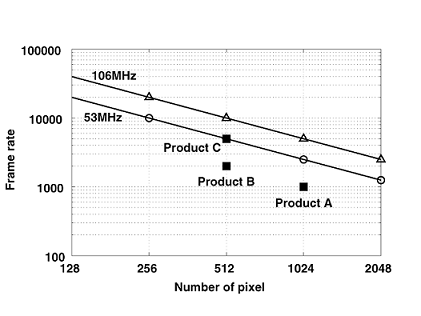

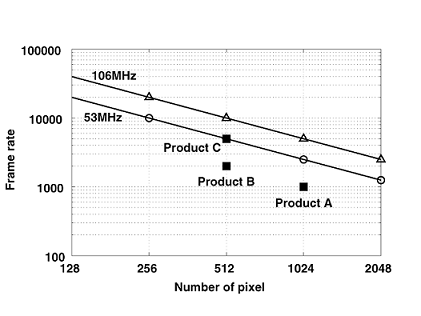

高速度イメージセンサに集積するための画像圧縮回路として,少ない回路規模と高い圧縮率を両立できるアルゴリズムを開発し,それを用いることでイメージアレイ出力から画像圧縮までを列並列処理で高速かつ少ないハードウェアで実現するアーキテクチャを提案しています.このアルゴリズムを用いることで,256x256画素,撮像速度10,000[frames/s]の高速度イメージセンサが画像圧縮を行う演算要素を16チャネル並列に実装することで実現可能であることを,論理合成,配置配線,ポストレイアウトシミュレーションから明らかにしました.このような高速度イメージセンサ上での画像圧縮の効果は,特に100万画素以上の高解像度かつ高速のイメージセンサの実現に有効であることを示し,100万画素の高解像度において,2,500[frames/s]というこれまでに報告されていない撮像速度の実現可能性を示した.

|

|

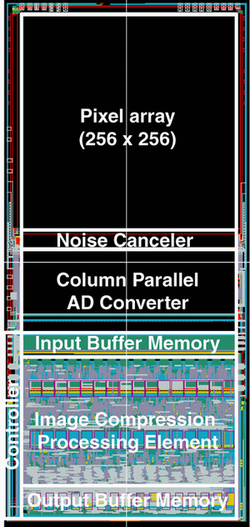

| 画像圧縮高速度イメージセンサの構成

| 画像圧縮回路を適用した場合に実現可能なフレームレートと解像度の関係

|

文献

- Y. Nishikawa, S. Kawahito, T. Inoue, " Parallel image compression circuits for high-speed cameras", Proc. SPIE Proc. Electronic Imaging, vol.5671, no.14, Jan. 2005.

- Y. Nishikawa, S. Kawahito, "A parallel image compression system for high-speed cameras", Proc. IEEE Int. Workshop on Imaging System and

Techniques, pp.53-57, May. 2005.

- Yukinari Nishikawa, Shoji Kawahito, Masanori Furuta, Toshihiro

Tamura, "Design of Parallel Image Compression Circuits for High-Speed CMOS Image Sensors", The Journal of the Institute of Image Information and Television Engineers, vol.61, no.3, pp.369-377, Mar. 2007.

[ホーム] / [研究プロジェクト一覧]

Copyright(C)1999-2007, Imaging Devices Laboratory

e-mail: [email protected]