低雑音読み出し回路

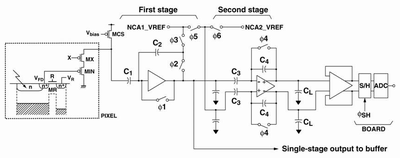

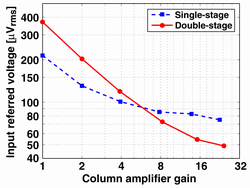

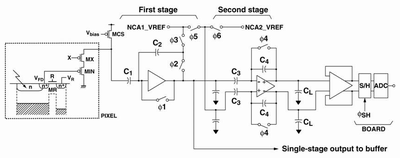

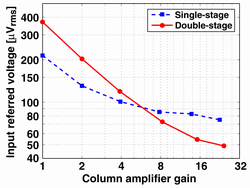

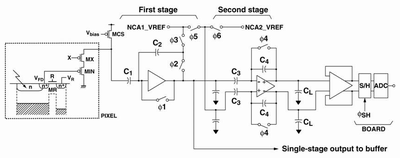

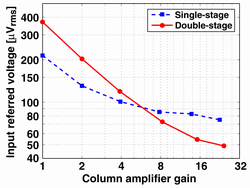

CMOSイメージセンサにおいて,カラムで高ゲインで増幅しながら,ノイズキャンセルアンプを2段で構成するダブルステージノイズキャンセルアーキテクチャーを用いることで,非常に低雑音(ノイズ)の信号読み出し回路を実現できることを見出しました.本アーキテクチャーに基づくCMOSラインイメージセンサを試作したところ,ゲインを高くすることで,1段のみの場合よりも2段構成の方が雑音を低減できることを実証し,雑音電圧として49.1uVrmsを達成しました.

|

|

| 試作したCMOSイメージセンサの信号読み出し回路

| 雑音低減効果

|

応用分野

本アーキテクチャーを適用したイメージセンサを用いることで,非常に高感度な撮像デバイスを構成することできます.それは,夜間の事件報道,セキュリティ,天文観察,微弱発光現象の検出などへの応用が期待されます.

文献

- N. Kawai, S. Kawahito,"Noise analysis of high-gain low-noise column readout circuits for CMOS image sensors", IEEE Trans. Electron Devices, Vol.51, No.2, pp.185-194, 2004

- N. Kawai and S. Kawahito, "Measurement of Low-Noise Column Readout Circuits for CMOS Image Sensors", IEEE Trans. Electron Devices, Vol.53, No.7, pp.1737-1739, 2006

[ホーム] / [研究プロジェクト一覧]

Copyright(C)1999-2007, Imaging Devices Laboratory

e-mail: [email protected]