高速低消費電力パイプラインA/D変換器

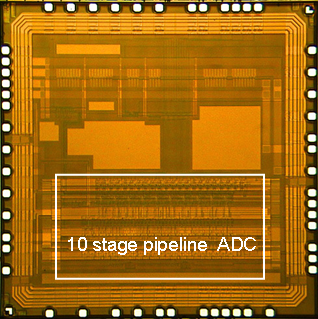

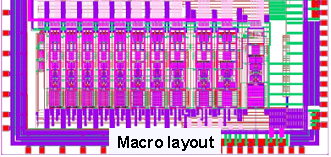

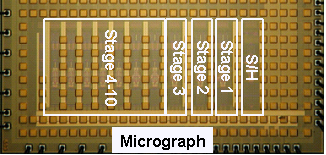

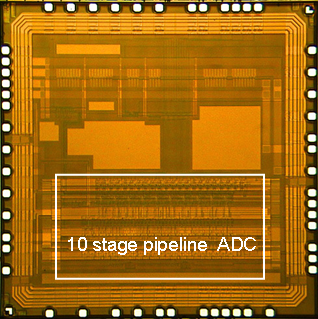

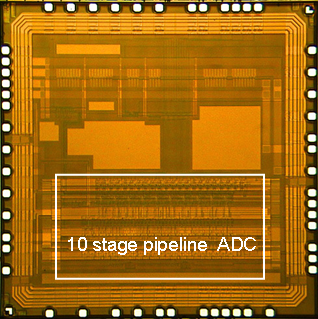

次世代映像機器、通信機器のキーデバイスである高速低消費電力パイプラインA/D変換器に関する研究を行っております。研究成果として、疑似差動アーキテクチャを用いた10ビット30MHzのA/D変換器を開発に成功しました。消費電力は16mW (Vdd=2.0V)であり、世界最高の電力効率(2002年当時)を達成しました。この成果は、2002年のISSCCで発表しております[1]。また、容量結合技術を用いた電源電圧1.0Vでの低歪・低消費電力A/D変換器も開発しており、90nmCMOSプロセスを用いた10bit 100MSample/s パイプラインA/D変換器では消費電力30mWを実現いたしました。2006年のSymp. on VLSI Circuitsでこの成果について発表しております[2]。

現在は高分解能なパイプラインA/D変換器の実現を目指し、研究を行っております。

|

|

| 16mW 10bit 30MSample/s パイプラインA/D変換器

| 1V 30mW 10bit 100MSample/s パイプラインA/D変換器

|

文献

- D. Miyazaki, M. Furuta, and S. Kawahito, "A 16mW 30Msample/s 10b Pipelined A/D Converter Using Pseudo Differential Architecture", Dig. of Tech. Papers, IEEE Int. Solid-State Circuits Conf., no.10.5, pp.174-175,Feb. 2002.

- D. Miyazaki, S. Kawahito, and M. Furuta, "A 10-b 30-MS/s Low-Power Pipelined CMOS A/D Converter Using a Pseudodifferential Architecture", IEEE Journal of Solid-State Circuits, Vol.38, No.2, pp.369-373, 2003.

- K. Honda, F. Masanori, and S. Kawahito, "A 1V 30mW 10b 100MSample/s Pipeline A/D Converter Using Capacitance Coupling Techniques", Proc. 2006 Symp. on VLSI Circuits, 25.4, Pp.276-277, Jun.2006.

- K. Honda, M. Furuta, and S. Kawahito, "A Low-Power Low-Voltage 10-bit 100-MSample/s Pipeline A/D Converter Using Capacitance Coupling Techniques", IEEE Journal of Solid-State Circuits, Vol.42, No.4, pp.-, 2007.

[ホーム] / [研究プロジェクト一覧]

Copyright(C)1999-2007, Imaging Devices Laboratory

e-mail: [email protected]