Gain mismatch, offset mismatch and timing error are three main mismatches in Time-interleaved Analog-to-Digital Converters(TiADCs). While there are effective methods to calibrate gain and offset mismatch already, timing error calibration is still under intensive research. Timing error is caused by sampling timing skew and RC(resistance of sampling switches and sampling capacitance) mismatch. Our research proved that the timing skew and RC mismatch can be calibrated simultaneously by adjusting clock phase. Ongoing research is emphasized on a practical background calibration method.

|

|

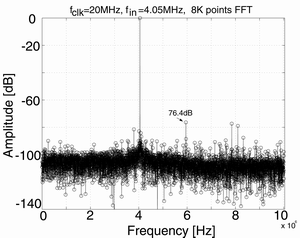

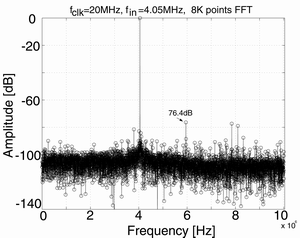

| Before timing error calibration. | After timing error calibration. |