A/Dコンバータのキャリブレーション手法

パイプラインA/D変換器内部のキャパシタミスマッチ測定回路が必要ないディジタルキャリブレーション手法について研究しています.

本手法はA/D変換器のディジタル出力より得られる積分非直線性誤差を用いてミスマッチの推定を行います.

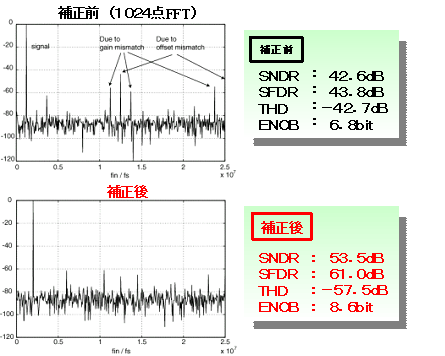

試作した10bit,120Msample/s,4並列パイプラインA/D変換器に本手法を応用した結果,実行分解能を約2bit向上できることを確認しました.

|

|

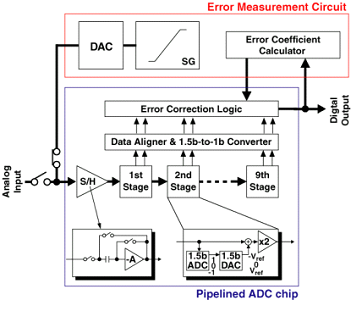

| ディジタルキャリブレーションアーキテクチャ

| キャパシタミスマッチディジタル補正効果

|

応用分野

本キャリブレーション手法では,様々なアーキテクチャのパイプラインA/D変換器に適用でき,また,製造後のA/D変換器に対してディジタル補正が可能であることから,工業用への応用が期待されます.

文献

- M. Furuta, S. Kawahito, D. Miyazaki, "A Digital Calibration Technique of Capacitor Mismatch for Pipelined Analog-to-Digital Converters", IEICE Trans. Electron., Vol.E85-C, No.8, pp.1562-1568, 2002

- D. Miyazaki, M. Furuta, S. Kawahito, "A 75mW 10bit 120Msample/s Parallel Piepline ADC", Proc. European Solid-State Circuits Conf., pp.719-722, 2003

- M. Furuta, S. Kawahito, D. Miyazaki, "A Digital Calibration Technique for Redundant Raidx-4 Pipelined Analog-to-Digital Converters", IEEE Trans. on Instrum. Meas., to be published

[ホーム] / [研究プロジェクト一覧]

Copyright(C)1999-2007, Imaging Devices Laboratory

e-mail: [email protected]